# MI920

Intel<sup>®</sup> Celeron<sup>®</sup> M 910GML Intel<sup>®</sup> Pentium<sup>®</sup> M/915GM Mini-ITX Motherboard

# **USER'S MANUAL**

Version 1.0A

# Acknowledgments

Award is a registered trademark of Award Software International, Inc.

PS/2 is a trademark of International Business Machines Corporation.

Intel and Pentium M are registered trademarks of Intel Corporation.

Microsoft Windows is a registered trademark of Microsoft Corporation.

Winbond is a registered trademark of Winbond Electronics Corporation.

All other product names or trademarks are properties of their respective owners.

# Table of Contents

| Introduction                                                                                                                                | 1        |

|---------------------------------------------------------------------------------------------------------------------------------------------|----------|

| Product Description<br>Checklist<br>MI920 Specifications                                                                                    | 2        |

| Board Dimensions                                                                                                                            |          |

| Installing the CPU<br>Installing the Memory<br>Setting the Jumpers                                                                          | 6<br>7   |

| Connectors on MI920 BIOS Setup                                                                                                              |          |

| Drivers Installation                                                                                                                        | 45       |

| Intel Chipset Software Installation Utility<br>VGA Drivers Installation<br>AC97 Codec Audio Driver Installation<br>LAN Drivers Installation | 49<br>52 |

| Appendix                                                                                                                                    | 56       |

| <ul><li>A. I/O Port Address Map</li><li>B. Interrupt Request Lines (IRQ)</li><li>C. Watchdog Timer Configuration</li></ul>                  | 57       |

MI920 User's Manual

iii

This page is intentionally left blank.

iv

# Introduction

# **Product Description**

The MI920 Mini ITX board incorporates the Mobile Intel® 910GML/915GM Express Chipset for Embedded Computing, consisting of the Intel® 910GML/ 915GM Graphic Memory Controller Hub (GMCH) and Intel® I/O Controller Hub 6-M (ICH6-M), is an optimized integrated graphics solution with a 400/533MHz front-side bus.

The integrated 32-bit 3D graphics engine, based on Intel® Graphics Media Accelerator 900 (Intel® GMA 900) architecture, operates at core speeds of up to 320 MHz. It features a low-power design, is validated with Intel® Pentium M/ Celeron® M processors on 130nm or 90nm process. With one DIMM socket on board, the board supports up to 1GB of DDR2 system memory (400MHz for 910GML, 400/533MHz for 915GM chipset).

Intel® Graphics supports a unique intelligent memory management scheme called Dynamic Video Memory Technology (DVMT). DVMT handles diverse applications by providing the maximum availability of system memory for general computer usage, while supplying additional graphics memory when a 3D-intensive application requests it. The Intel GMA 900 graphics architecture also takes advantage of the high-performance Intel processor. Intel GMA 900 graphics supports Dual Independent Display technology.

The main features of the board are:

- Supports Celeron® M processors, 400MHz FSB (910GML chipset)

- Supports Socket 479, 533/400MHz FSB (915GM chipset)

- One DDRII SDRAM DIMM supports up to 1GB of DDR2 400MHz (910GML chipset), DDR2 400/533MHz (915GM chipset)

- Onboard 10/100 BaseT and Marvell PCI-Express Gigabit LAN

- Intel® 915 Express VGA for CRT, SDVO port supports LVDS and DVI / LVDS

- 2x SATA, 6x USB 2.0, 4x COM, Watchdog timer

- 1x PCI, 1x MiniPCIe, CF socket, DC-in for +12V input

Dimensions of the board are 170mm x 170mm.

Ordering Information:

MI920F: Socket 479, 915GM, ICH6M, supports DVI, LVDS, 1x 10/100 LAN, 1x Gigabit LAN, Mini PCI-E MI920L-C6K: Celeron M 600M/512K , 910GML, ICH6M, supports DVI, LVDS, 1x 10/100 LAN

MI920 User's Manual

# Checklist

Your MI920 package should include the items listed below.

- The MI920 Celeron® M Mini-ITX motherboard

- This User's Manual

- 1 CD containing chipset drivers and flash memory utility

- Cable kit (IDE, Serial port, Serial ATA, VGA)

2

3

# **MI920** Specifications

| Form Factor         | Mini ITX                                                                                                              |  |  |

|---------------------|-----------------------------------------------------------------------------------------------------------------------|--|--|

| CPU Type            | Intel Celeron M / Pentium M (on Socket 479) processor (Banias or                                                      |  |  |

|                     | Dothan core):                                                                                                         |  |  |

|                     | - Banias: ULV Celeron M 600MHz (512KB L2 Cache),                                                                      |  |  |

|                     | - Dothan: Zero L2 cache Celeron M 1GHz or Celeron M 373                                                               |  |  |

| CPU Voltage         | 0.700V ~ 1.708V                                                                                                       |  |  |

| CPU FSB             | 400MHz (910GML); 400/533MHz (915GM)                                                                                   |  |  |

| CPU Socket          | Socket 479 co-layout with micro-FCBGA                                                                                 |  |  |

| Chipset             | Intel 910GML/915GM chipset                                                                                            |  |  |

| empeer              | ICH6M: 82801FBM                                                                                                       |  |  |

| BIOS /APM           | Award BIOS, support ACPI Function & APM1.2                                                                            |  |  |

| Memory              | DDRII 400/533 SDRAM DIMM socket x1 (w/o ECC function), Max.                                                           |  |  |

| wennory             | 1GB                                                                                                                   |  |  |

| VGA                 | 910GML built-in, supports dual display with CRT, LVDS & TV-Out                                                        |  |  |

| DVI                 | Chrontel CH7307 x1 for DVI                                                                                            |  |  |

| LVDS                |                                                                                                                       |  |  |

|                     | Chrontel CH7308 x1 for 18 or 24-bit single/dual channel LVDS<br>LAN1: ICH6M built-in 10/100BT MAC + Intel 82562ET PHY |  |  |

| LAN                 |                                                                                                                       |  |  |

| 1100                | Optional LAN2: Marvell 88E8053 PCI Express Gigabit LAN controller                                                     |  |  |

| USB                 | ICH6M built-in USB 2.0 host controller, support 6 ports                                                               |  |  |

| Serial ATA          | ICH6M built-in SATA controller, supports 2 ports                                                                      |  |  |

| Parallel IDE        | ICH6M built-in one channel Ultra DMA 33/66/100 for IDE & CF                                                           |  |  |

| Audio               | ICH6M built-in Audio controller + AC97 Codec ALC655 w/ 6 channels                                                     |  |  |

|                     | (Line-out, Line-in & Mic.) + ADI SSM2304 40hm 2W, class D, stereo                                                     |  |  |

|                     | audio power amplifier (note: 1.4W for 8 ohm)                                                                          |  |  |

| LPC I/O             | Winbond W83627EHG: PS/2 Keyboard/Mouse, 2x serial (RS232) &                                                           |  |  |

|                     | Hardware monitor (3 thermal inputs, 4 voltage monitor inputs,                                                         |  |  |

|                     | VID0-4 & 2 fan headers)                                                                                               |  |  |

| 2 <sup>nd</sup> I/O | Fintek F81216DG x1 for COM3, 4 (RS-232)                                                                               |  |  |

| Expansion Slots     | PCI (33MHz/32-bit) slot x1                                                                                            |  |  |

|                     | Optional Mini PCI-express (1 lane) socket x1 (for wireless module)                                                    |  |  |

| Edge                | DC-in power connector (Jack type) x1                                                                                  |  |  |

| Connectors          | PS/2 stack connector x1 for keyboard/mouse                                                                            |  |  |

|                     | DVI + DB9 stack connector x1 for DVI & COM 1                                                                          |  |  |

|                     | RJ45 (10/100) + dual USB stack connector x1 for LAN1 & USB1, 2                                                        |  |  |

|                     | S-Video connector x1 for S-Video                                                                                      |  |  |

|                     | RJ45 (GbE) + dual USB stack connector x1 for LAN2 & USB3, 4                                                           |  |  |

|                     | *** Option with dual USB stack connector (LAN2 option)                                                                |  |  |

|                     | 3x1 phone jack stack connector x1 for Audio (Line-Out, Line-In & Mic)                                                 |  |  |

| Onboard             | Compact flash socket (vertical type) x1 @component side                                                               |  |  |

| Headers /           | SATA connector x2 for 2 SATA ports                                                                                    |  |  |

| Connectors          | DF13-20 (20-pin) header x2 for LVDS                                                                                   |  |  |

|                     | 15 pins pin-header x1 for VGA                                                                                         |  |  |

|                     | 40 pins box-header x1 for IDE                                                                                         |  |  |

|                     | 30 pins pin-header x1 for COM2~4                                                                                      |  |  |

|                     | 8 pins pin-header x1 for USB 5~6                                                                                      |  |  |

|                     | 3 pins pin-header x1 for power LED                                                                                    |  |  |

|                     | 6 pins pin-header x1 for Reset, HDD LED & power button                                                                |  |  |

| Watchdog Timer      | Yes (256 segments, 0, 1, 2255 sec/min)                                                                                |  |  |

| System Voltage      | +5V, +3.3V, +12V, -12V, 5VSB                                                                                          |  |  |

| Other               | LAN Wakeup                                                                                                            |  |  |

| Digital I/O         | 4 in + 4 out (TTL level)                                                                                              |  |  |

| Power In / Out      | Power Input: +12V DC power input                                                                                      |  |  |

|                     | Power Output: 4-pin power connector x1 for HDD/CD-ROM/DVD                                                             |  |  |

| Board Size          | 170mm x 170mm                                                                                                         |  |  |

| 20010 0120          |                                                                                                                       |  |  |

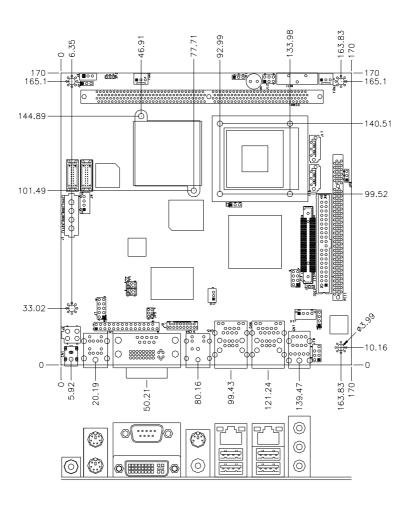

# **Board Dimensions**

MI920 User's Manual

5

# Installations

This section provides information on how to use the jumpers and connectors on the MI920 in order to set up a workable system. The topics covered are:

| Installing the CPU    | 6  |

|-----------------------|----|

| Installing the Memory | 7  |

| Setting the Jumpers   | 8  |

| Connectors on MI920   | 12 |

|                       |    |

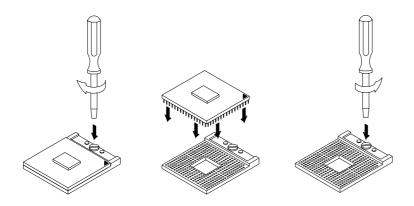

# **Installing the CPU**

The MI920 board supports a Socket 479 processor socket for Intel<sup>®</sup> Pentium<sup>®</sup> M or Celeron<sup>®</sup> M processors.

The processor socket comes with a screw to secure the processor. As shown in the left picture below, loosen the screw first before inserting the processor. Place the processor into the socket by making sure the notch on the corner of the CPU corresponds with the notch on the inside of the socket. Once the processor has slide into the socket, fasten the screw. Refer to the figures below.

**NOTE:** Ensure that the CPU heat sink and the CPU top surface are in total contact to avoid CPU overheating problem that would cause your system to hang or be unstable.

6

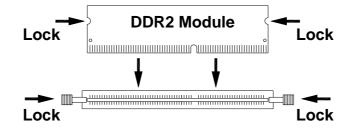

# **Installing the Memory**

The MI920 board supports one DDR2 memory socket for a maximum total memory of 1GB in DDR2 memory type.

#### **Installing and Removing Memory Modules**

To install the DDR2 modules, locate the memory slot on the board and perform the following steps:

- 1. Hold the DDR2 module so that the key of the DDR2 module align with those on the memory slot.

- 2. Gently push the DDR2 module in an upright position until the clips of the slot close to hold the DDR2 module in place when the DDR2 module touches the bottom of the slot.

- 3. To remove the DDR2 module, press the clips with both hands.

MI920 User's Manual

# Setting the Jumpers

Jumpers are used on MI920 to select various settings and features according to your needs and applications. Contact your supplier if you have doubts about the best configuration for your needs. The following lists the connectors on MI920 and their respective functions.

| Jumper Locations on MI920                     | 9  |

|-----------------------------------------------|----|

| JP1: LCD Panel Power Selection                | 10 |

| JP8: Clear CMOS Setting                       | 10 |

| JP7: CompactFlash Slave/Master Selection      |    |

| JP2: ATX/AT Mode Select                       | 10 |

| JP3: COM3 RS232 +5V / +12V Power Setting      | 10 |

| JP4: COM4 RS232 +5V / +12V Power Setting      | 11 |

| JP5: VGA/DVI DDCDATA and DDCCLK Signal Select | 11 |

| JP6: CPU FSB Selection (915GM only)           | 11 |

|                                               |    |

# Jumper Locations on MI920

| Jumpers on MI920                              | Page |

|-----------------------------------------------|------|

| JP1: LCD Panel Power Selection                | 10   |

| JP8: Clear CMOS Setting                       | 10   |

| JP7: CompactFlash Slave/Master Selection      | 10   |

| JP2: ATX/AT Mode Select                       | 10   |

| JP3: COM3 RS232 +5V / +12V Power Setting      | 10   |

| JP4: COM4 RS232 +5V / +12V Power Setting      | 11   |

| JP5: VGA/DVI DDCDATA and DDCCLK Signal Select | 11   |

| JP6: CPU FSB Selection (915GM only)           | 11   |

|                                               |      |

MI920 User's Manual

# JP1: LCD Panel Power Selection

| JP1 | LCD Panel Power |

|-----|-----------------|

| 123 | 3.3V            |

| 123 | 5V              |

# JP8: Clear CMOS Setting

| JP8        | Setting    |  |

|------------|------------|--|

| •••<br>123 | Normal     |  |

| 123        | Clear CMOS |  |

# JP7: CompactFlash Slave/Master Selection

| JP7         | CF Setting |

|-------------|------------|

| Short       | Master     |

| o o<br>Open | Slave      |

# JP2: ATX/AT Mode Select

| JP2 | ATX / AT |

|-----|----------|

| 123 | ATX mode |

| 123 | AT mode  |

# JP3: COM3 RS232 +5V / +12V Power Setting

| Pin # | Signal Name  | JP3                | Signal Name  | Pin # |

|-------|--------------|--------------------|--------------|-------|

| 1     | RI           | 1                  | +12V         | 2     |

| 3     | RI (Default) | 1 = = 2<br>5 = = 6 | RI (Default) | 4     |

| 5     | RI           | 5006               | +5V          | 6     |

COM3 Settings: Pin 1-2 short = +12V, Pin 5-6 short = +5V, Pin 3-4 Standard COM Port

10

# JP4: COM4 RS232 +5V / +12V Power Setting

| Pin # | Signal Name  | JP4  | Signal Name  | Pin # |

|-------|--------------|------|--------------|-------|

| 1     | RI           | 1    | +12V         | 2     |

| 3     | RI (Default) | 1002 | RI (Default) | 4     |

| 5     | RI           | 1000 | +5V          | 6     |

COM4 Settings: Pin 1-2 short = +12V, Pin 5-6 short = +5V, Pin 3-4 Standard COM Port

# JP5: VGA/DVI DDCDATA and DDCCLK Signal Select

| JP5                                                                                           | VGA/DVI Select |

|-----------------------------------------------------------------------------------------------|----------------|

| $2 \bigcirc 6$ $1 \bigcirc 5$                                                                 | VGA            |

| $\begin{array}{c} 2 \\ 1 \\ \hline \end{array} \begin{array}{c} 6 \\ 5 \\ \hline \end{array}$ | DVI            |

# JP6: CPU FSB Selection (915GM only)

| JP6 | FSB    |

|-----|--------|

| 123 | 400MHz |

| 123 | 533MHz |

MI920 User's Manual

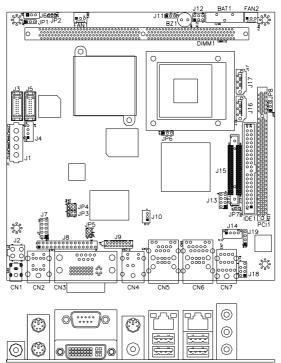

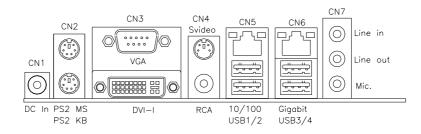

# **Connectors on MI920**

The connectors on MI920 allows you to connect external devices such as keyboard, floppy disk drives, hard disk drives, printers, etc. The following table lists the connectors on MI920 and their respective functions.

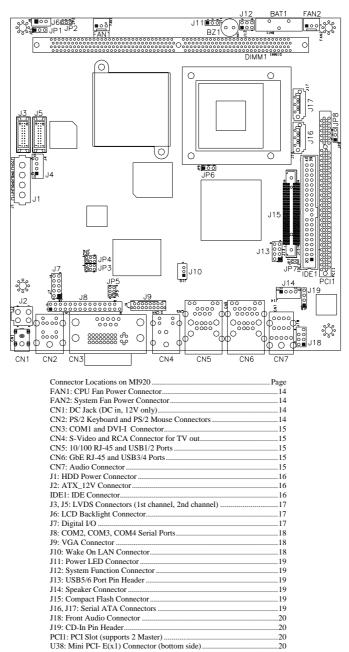

| a                                                  |

|----------------------------------------------------|

| Connector Locations on MI920                       |

| FAN1: CPU Fan Power Connector14                    |

| FAN2: System Fan Power Connector14                 |

| CN1: DC Jack (DC in, 12V only)14                   |

| CN2: PS/2 Keyboard and PS/2 Mouse Connectors       |

| CN3: COM1 and DVI-I Connector                      |

| CN4: S-Video and RCA Connector for TV out15        |

| CN5: 10/100 RJ-45 and USB1/2 Ports                 |

| CN6: GbE RJ-45 and USB3/4 Ports15                  |

| CN7: Audio Connector                               |

| J1: HDD Power Connector                            |

| J2: ATX 12V Connector                              |

| IDE1: IDE Connector                                |

| J3, J5: LVDS Connectors (1st channel, 2nd channel) |

| J6: LCD Backlight Connector17                      |

| J7: Digital I/O                                    |

| J8: COM2, COM3, COM4 Serial Ports                  |

| J9: VGA Connector                                  |

| J10: Wake On LAN Connector                         |

| J11: Power LED Connector                           |

| J12: System Function Connector                     |

| J13: USB5/6 Port Pin Header                        |

| J14: Speaker Connector                             |

| J15: Compact Flash Connector                       |

| J16, J17: Serial ATA Connectors                    |

| J18: Front Audio Connector                         |

| J19: CD-In Pin Header                              |

| PCI1: PCI Slot (supports 2 Master)                 |

| U38: Mini PCI- E(x1) Connector (bottom side)       |

|                                                    |

MI920 User's Manual

#### **Connector Locations on MI920**

MI920 User's Manual

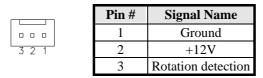

## FAN1: CPU Fan Power Connector

FAN1 is a 3-pin header for the CPU fan. The fan must be a 12V fan.

|     | Pin # | Signal Name        |

|-----|-------|--------------------|

|     | 1     | Ground             |

| 321 | 2     | +12V               |

|     | 3     | Rotation detection |

# FAN2: System Fan Power Connector

FAN2 is a 3-pin header for system fans. The fan must be 12V (500mA).

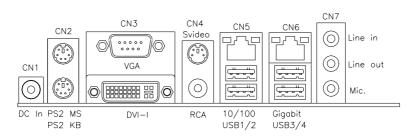

# CN1: DC Jack (DC in, 12V only)

# CN2: PS/2 Keyboard and PS/2 Mouse Connectors

| Signal Name    | Keyboard | Mouse | Signal Name |

|----------------|----------|-------|-------------|

| Keyboard data  | 1        | 1     | Mouse data  |

| N.C.           | 2        | 2     | N.C.        |

| GND            | 3        | 3     | GND         |

| 5V             | 4        | 4     | 5V          |

| Keyboard clock | 5        | 5     | Mouse clock |

| N.C.           | 6        | 6     | N.C.        |

14

CN3: COM1 and DVI-I Connector

|       |    | Signal Name Pin # |       | # | Pin # | Signal Name |

|-------|----|-------------------|-------|---|-------|-------------|

| 1, ,5 | 5  | DCD               | 1     |   | 6     | DSR         |

|       | ~  | RXD               | 2     | 2 |       | RTS         |

|       | _  | TXD               | 3     |   | 8     | CTS         |

| 6´``9 |    | DTR               | 4     |   | 9     | RI          |

|       |    | GND               | 5     |   | 10    | Not Used    |

|       | Si | gnal Name         | Pin # |   | Pin # | Signal Name |

|       |    | DATA 2-           | 1     |   | 16    | HOT POWER   |

| e e   |    | DATA 2+           | 2     |   | 17    | DATA 0-     |

|       |    | Shield 2/4        | 3     |   | 18    | DATA 0+     |

|       |    | DATA 4-           | 4     |   | 19    | SHIELD 0/5  |

|       |    | DATA 4+           | 5     |   | 20    | DATA 5-     |

| ×     | D  | DC CLOCK          | 6     |   | 21    | DATA 5+     |

|       | D  | DC DATA           | 7     |   | 22    | SHIELD CLK  |

|       |    | VSYNC             | 8     |   | 23    | CLOCK -     |

|       |    | DATA 1-           | 9     |   | 24    | CLOCK +     |

| 5 Q   |    | DATA 1+           | 10    |   | C1    | A RED       |

|       | S  | HIELD 1/3         | 11    |   | C2    | A GREEN     |

|       |    | DATA 3-           | 12    |   | C3    | A BLUE      |

|       |    | DATA 3+           | 13    |   | C4    | HYNC        |

|       | D  | DC POWER          | 14    |   | C5    | A GROUND2   |

|       | Α  | GROUND 1          | 15    |   | C6    | A GROUND3   |

CN4: S-Video and RCA Connector for TV out

CN5: 10/100 RJ-45 and USB1/2 Ports

CN6: GbE RJ-45 and USB3/4 Ports

**CN7: Audio Connector**

MI920 User's Manual

# J1: HDD Power Connector

|      | Pin # | Signal Name |

|------|-------|-------------|

| 0    | 1     | +12V        |

| 04   | 2     | Ground      |

| لے ّ | 3     | Ground      |

|      | 4     | 5V          |

Note: +12V power is provided with 2A maximum load.

# J2: ATX\_12V Connector

J2 can be used in situations where the 12V current from the ATX power is insufficient to supply needed current.

|         | Pin # | Signal Name |

|---------|-------|-------------|

| 1 6 0 2 | 1     | Ground      |

| 3004    | 2     | Ground      |

|         | 3     | +12V        |

|         | 4     | +12V        |

# **IDE1: IDE Connector**

|           | Signal Name   | Pin # | Pin # | Signal Name   |

|-----------|---------------|-------|-------|---------------|

|           | Reset IDE     | 1     | 2     | Ground        |

|           | Host data 7   | 3     | 4     | Host data 8   |

| 1 - 2     | Host data 6   | 5     | 6     | Host data 9   |

|           | Host data 5   | 7     | 8     | Host data 10  |

|           | Host data 4   | 9     | 10    | Host data 11  |

|           | Host data 3   | 11    | 12    | Host data 12  |

|           | Host data 2   | 13    | 14    | Host data 13  |

|           | Host data 1   | 15    | 16    | Host data 14  |

|           | Host data 0   | 17    | 18    | Host data 15  |

|           | Ground        | 19    | 20    | Protect pin   |

|           | DRQ0          | 21    | 22    | Ground        |

|           | Host IOW      | 23    | 24    | Ground        |

|           | Host IOR      | 25    | 26    | Ground        |

|           | IOCHRDY       | 27    | 28    | Host ALE      |

| 39 0 0 40 | DACK0         | 29    | 30    | Ground        |

|           | IRQ14         | 31    | 32    | No connect    |

|           | Address 1     | 33    | 34    | No connect    |

|           | Address 0     | 35    | 36    | Address 2     |

|           | Chip select 0 | 37    | 38    | Chip select 1 |

|           | Activity      | 39    | 40    | Ground        |

16

J3, J5: LVDS Connectors (1st channel, 2nd channel) The LVDS connectors on board consist of the first channel (J3) and second channel (J5) and supports 18-bit or 24-bit.

|         | Signal Name | Pin # | Pin # | Signal Name |

|---------|-------------|-------|-------|-------------|

|         | TX0-        | 2     | 1     | TX0+        |

| 2 • • 1 | Ground      | 4     | 3     | Ground      |

|         | TX1-        | 6     | 5     | TX1+        |

| 0 0     | 5V/3.3V     | 8     | 7     | Ground      |

|         | TX3-        | 10    | 9     | TX3+        |

| 0 0     | TX2-        | 12    | 11    | TX2+        |

|         | Ground      | 14    | 13    | Ground      |

| 20 - 19 | TXC-        | 16    | 15    | TXC+        |

|         | 5V/3.3V     | 18    | 17    | ENABKL      |

|         | +12V        | 20    | 19    | +12V        |

# J6: LCD Backlight Connector

|     | Pin # | Signal Name      |

|-----|-------|------------------|

| 1 🗖 | 1     | +12V             |

| 30  | 2     | Backlight Enable |

|     | 3     | Ground           |

# J7: Digital I/O

|         | Signal Name | Pin | Pin | Signal Name |

|---------|-------------|-----|-----|-------------|

| 1 🔳 O 2 | GND         | 1   | 2   | VCC         |

|         | OUT3        | 3   | 4   | OUT1        |

| 90010   | OUT2        | 5   | 6   | OUT0        |

| 30010   | IN3         | 7   | 8   | IN1         |

|         | IN2         | 9   | 10  | IN0         |

MI920 User's Manual

# J8: COM2, COM3, COM4 Serial Ports

| 6 |   |    |   | 10 | 6 |   |    | 1  | 0 | 6 |   |    | 1  | 0 |

|---|---|----|---|----|---|---|----|----|---|---|---|----|----|---|

|   |   |    |   |    |   |   |    |    |   |   |   |    |    |   |

|   |   |    |   |    |   |   |    |    |   |   |   |    |    |   |

| 1 | С | ΟМ | 2 | 5  | 1 | С | ٥N | 13 | 5 | 1 | С | ٥N | 14 | 5 |

| Pin # | Signal Name (RS-232)     |

|-------|--------------------------|

| 1     | DCD, Data carrier detect |

| 2     | RXD, Receive data        |

| 3     | TXD, Transmit data       |

| 4     | DTR, Data terminal ready |

| 5     | Ground                   |

| 6     | DSR, Data set ready      |

| 7     | RTS, Request to send     |

| 8     | CTS, Clear to send       |

| 9     | RI, Ring indicator       |

| 10    | No Connect.              |

# **J9: VGA Connector**

16

|         |   | Signal Name | Pin # | Pin # | Signal Name |

|---------|---|-------------|-------|-------|-------------|

| 2 🗖 🗖 1 |   | +5V         | 2     | 1     | RED         |

|         |   | Ground      | 4     | 3     | GREEN       |

|         |   | N.C.        | 6     | 5     | BLUE        |

|         |   | SDA         | 8     | 7     | N.C.        |

|         |   | HSYNC       | 10    | 9     | Ground      |

|         | 5 | VSYNC       | 12    | 11    | Ground      |

|         | 0 | SCL         | 14    | 13    | Ground      |

|         |   | N.C.        | 16    | 15    | Ground      |

# J10: Wake On LAN Connector

3

J10 is a 3-pin header for the Wake On LAN function. Wake On LAN will function properly only with an ATX power supply with 5VSB that has 200mA.

| 0 1 | Pin # | Signal Name |

|-----|-------|-------------|

|     | 1     | +5VSB       |

|     | 2     | Ground      |

|     | 3     | -PME        |

18

# J11: Power LED Connector

|   | Pin # | Signal Name |

|---|-------|-------------|

|   | 1     | Vcc         |

| 0 | 2     | NC          |

|   | 3     | PLED        |

# J12: System Function Connector

| <br>Signal Name | Pin | Pin | Signal Name |

|-----------------|-----|-----|-------------|

| Ground          | 1   | 2   | PS_ON       |

| 5V              | 3   | 4   | HDD Active  |

| Ground          | 5   | 7   | Reset       |

ATX power on switch: Pins 1-2 HDD LED: Pins 3-4 Reset switch: Pins 5-6

# J13: USB5/6 Port Pin Header

|         | Signal Name | Pin | Pin | Signal Name |

|---------|-------------|-----|-----|-------------|

| 1 🗖 0 5 | Vcc         | 1   | 5   | Ground      |

| 00      | D-          | 2   | 6   | D+          |

| 4008    | D+          | 3   | 7   | D-          |

|         | Ground      | 4   | 8   | Vcc         |

### J14: Speaker Connector

The J14 connector supports 2W/80hm stereo audio power amplifier.

|     | Pin # | Signal Name |

|-----|-------|-------------|

| 10  | 1     | Audio L     |

|     | 2     | Ground      |

| 4 🗆 | 3     | Ground      |

|     | 4     | Audio R     |

J15: Compact Flash Connector

J16, J17: Serial ATA Connectors

MI920 User's Manual

# J18: Front Audio Connector

|       | Signal Name   | Pin | Pin | Signal Name   |

|-------|---------------|-----|-----|---------------|

| 1 0 2 | Rear Audio R  | 1   | 5   | Rear Audio L  |

| 00    | Front Audio R | 2   | 6   | Front Audio L |

| 7008  | Mic In        | 3   | 7   | VREF Out      |

|       | Ground        | 4   | 8   |               |

**REMARKS:** To use the front audio connector, the jumpers on pin 1-3 and pin 2-4 must be removed.

# J19: CD-In Pin Header

| 10 | Pin # | Signal Name |

|----|-------|-------------|

|    | 1     | CD Audio R  |

|    | 2     | Ground      |

| 4  | 3     | Ground      |

|    | 4     | CD Audio L  |

PCI1: PCI Slot (supports 2 Master)

U38: Mini PCI- E(x1) Connector (bottom side)

20

21

# **BIOS Setup**

This chapter describes the different settings available in the Award BIOS that comes with the board. The topics covered in this chapter are as follows:

| BIOS Introduction            | 22 |

|------------------------------|----|

| BIOS Setup                   | 22 |

| Standard CMOS Setup          | 24 |

| Advanced BIOS Features       | 27 |

| Advanced Chipset Features    | 30 |

| Integrated Peripherals       | 33 |

| Power Management Setup       | 37 |

| PNP/PCI Configurations       | 40 |

| PC Health Status             | 41 |

| Frequency/Voltage Control    | 42 |

| Load Fail-Safe Defaults      |    |

| Load Optimized Defaults      | 43 |

| Set Supervisor/User Password | 43 |

| Save & Exit Setup            | 43 |

| Exit Without Saving          |    |

|                              |    |

#### **BIOS Introduction**

The Award BIOS (Basic Input/Output System) installed in your computer system's ROM supports Intel processors. The BIOS provides critical low-level support for a standard device such as disk drives, serial ports and parallel ports. It also adds virus and password protection as well as special support for detailed fine-tuning of the chipset controlling the entire system.

### **BIOS Setup**

The Award BIOS provides a Setup utility program for specifying the system configurations and settings. The BIOS ROM of the system stores the Setup utility. When you turn on the computer, the Award BIOS is immediately activated. Pressing the <Del> key immediately allows you to enter the Setup utility. If you are a little bit late pressing the <Del> key, POST (Power On Self Test) will continue with its test routines, thus preventing you from invoking the Setup. If you still wish to enter Setup, restart the system by pressing the "Reset" button or simultaneously pressing the <Ctrl>, <Alt> and <Delete> keys. You can also restart by turning the system Off and back On again. The following message will appear on the screen:

Press <DEL> to Enter Setup

In general, you press the arrow keys to highlight items, <Enter> to select, the <PgUp> and <PgDn> keys to change entries, <F1> for help and <Esc> to quit.

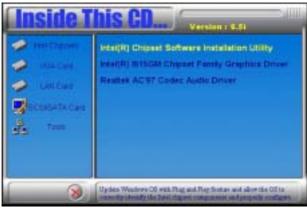

When you enter the Setup utility, the Main Menu screen will appear on the screen. The Main Menu allows you to select from various setup functions and exit choices.

22

| Phoenix - AwardBIOS CMOS Setup Utility |                                                   |  |  |

|----------------------------------------|---------------------------------------------------|--|--|

| Standard CMOS Features                 | Frequency/Voltage Control                         |  |  |

| Advanced BIOS Features                 | Load Fail-Safe Defaults                           |  |  |

| Advanced Chipset Features              | Load Optimized Defaults                           |  |  |

| Integrated Peripherals                 | Set Supervisor Password                           |  |  |

| Power Management Setup                 | Set User Password                                 |  |  |

| PnP/PCI Configurations                 | Save & Exit Setup                                 |  |  |

| PC Health Status                       | Exit Without Saving                               |  |  |

| ESC : Quit                             | $\land \lor \rightarrow \leftarrow$ : Select Item |  |  |

| F10 : Save & Exit Setup                |                                                   |  |  |

| Time, Date, Hard Disk Type             |                                                   |  |  |

The section below the setup items of the Main Menu displays the control keys for this menu. At the bottom of the Main Menu just below the control keys section, there is another section, which displays information on the currently highlighted item in the list.

- *Note:* If the system cannot boot after making and saving system changes with Setup, the Award BIOS supports an override to the CMOS settings that resets your system to its default.

- *Warning:* It is strongly recommended that you avoid making any changes to the chipset defaults. These defaults have been carefully chosen by both Award and your system manufacturer to provide the absolute maximum performance and reliability. Changing the defaults could cause the system to become unstable and crash in some cases.

MI920 User's Manual

# Standard CMOS Setup

"Standard CMOS Setup" choice allows you to record some basic hardware configurations in your computer system and set the system clock and error handling. If the motherboard is already installed in a working system, you will not need to select this option. You will need to run the Standard CMOS option, however, if you change your system hardware configurations, the onboard battery fails, or the configuration stored in the CMOS memory was lost or damaged.

Phoenix - AwardBIOS CMOS Setup Utility

|                                                                                                                                                      | Standard CMOS Features |                        |

|------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|------------------------|

| Date (mm:dd:yy)                                                                                                                                      | Fri, Mar 23, 2007      | Item Help              |

| Time (hh:mm:ss)                                                                                                                                      | 00 : 00 : 00           | Menu Level >           |

|                                                                                                                                                      |                        |                        |

| IDE Channel 0 Master                                                                                                                                 | None                   | Change the day, month, |

| IDE Channel 0 Slave                                                                                                                                  | None                   | Year and century       |

| IDE Channel 1 Master                                                                                                                                 | None                   |                        |

| IDE Channel 1 Slave                                                                                                                                  | None                   |                        |

| Date (mm:dd:yy)<br>Time (hh:mm:ss)<br>IDE Channel 0 Master<br>IDE Channel 0 Slave<br>IDE Channel 1 Master<br>IDE Channel 1 Slave<br>Video<br>Halt On | EGA/VGA                |                        |

| Halt On                                                                                                                                              | All, But Keyboard      |                        |

|                                                                                                                                                      | All, But Reyboard      |                        |

| Base Memory                                                                                                                                          | 640K                   |                        |

| Extended Memory                                                                                                                                      | 514048K                |                        |

| Total Memory                                                                                                                                         | 515072K                |                        |

At the bottom of the menu are the control keys for use on this menu. If you need any help in each item field, you can press the  $\langle F1 \rangle$  key. It will display the relevant information to help you. The memory display at the lower right-hand side of the menu is read-only. It will adjust automatically according to the memory changed. The following describes each item of this menu.

#### Date

The date format is:

| Day :   | Sun to Sat   |

|---------|--------------|

| Month : | 1 to 12      |

| Date :  | 1 to 31      |

| Year :  | 1999 to 2099 |

To set the date, highlight the "Date" field and use the PageUp/ PageDown or +/- keys to set the current time.

24

#### Time

The time format is: Hour : 00 to 23 Minute : 00 to 59 Second : 00 to 59

To set the time, highlight the "Time" field and use the  $\langle PgUp \rangle / \langle PgDn \rangle$  or +/- keys to set the current time.

#### **IDE Channel Master/Slave**

The onboard PCI IDE connector provides Primary and Secondary channels for connecting up to two IDE hard disks or other IDE devices.

Press <Enter> to configure the hard disk. The selections include Auto, Manual, and None. Select 'Manual' to define the drive information manually. You will be asked to enter the following items.

| Capacity :       | Capacity/size of the hard disk drive |

|------------------|--------------------------------------|

| CYLS :           | Number of cylinders                  |

| HEAD :           | Number of read/write heads           |

| <b>PRECOMP</b> : | Write precompensation                |

| LANDING ZONE :   | Landing zone                         |

| SECTOR :         | Number of sectors                    |

The Access Mode selections are as follows:

| CHS   | (HD < 528MB)              |

|-------|---------------------------|

| LBA   | (HD > 528MB and supports  |

|       | Logical Block Addressing) |

| Large | (for MS-DOS only)         |

| Auto  |                           |

**Remarks**: The main board supports two serial ATA ports and are represented in this setting as IDE Channel 0.

#### Video

This field selects the type of video display card installed in your system. You can choose the following video display cards:

| EGA/VGA | For EGA, VGA, SEGA, SVGA           |

|---------|------------------------------------|

|         | or PGA monitor adapters. (default) |

| CGA 40  | Power up in 40 column mode.        |

| CGA 80  | Power up in 80 column mode.        |

| MONO    | For Hercules or MDA adapters.      |

MI920 User's Manual

# Halt On

This field determines whether or not the system will halt if an error is detected during power up.

| 01                | 1                                                 |  |

|-------------------|---------------------------------------------------|--|

| No errors         | The system boot will not be halted for any error  |  |

|                   | that may be detected.                             |  |

| All errors        | Whenever the BIOS detects a non-fatal error,      |  |

|                   | the system will stop and you will be prompted.    |  |

| All, But Keyboard | The system boot will not be halted for a          |  |

|                   | keyboard error; it will stop for all other errors |  |

| All, But Diskette | The system boot will not be halted for a disk     |  |

|                   | error; it will stop for all other errors.         |  |

| All, But Disk/Key | The system boot will not be halted for a key-     |  |

|                   | board or disk error; it will stop for all others. |  |

|                   |                                                   |  |

# **Advanced BIOS Features**

This section allows you to configure and improve your system and allows you to set up some system features according to your preference.

| CPU Feature                | Press Enter | ITEM HELP    |

|----------------------------|-------------|--------------|

| Hard Disk Boot Priority    | Press Enter |              |

| Virus Warning              | Disabled    | Menu Level > |

| CPU L1 and L2 Cache        | Enabled     |              |

| Quick Power On Self Test   | Enabled     |              |

| First Boot Device          | Hard Disk   |              |

| Second Boot Device         | CDROM       |              |

| Third Boot Device          | USB-FDD     |              |

| Boot Other Device          | Enabled     |              |

| Boot Up NumLock Status     | On          |              |

| Gate A20 Option            | Fast        |              |

| Typematic Rate Setting     | Disabled    |              |

| Typematic Rate (Chars/Sec) | 6           |              |

| Typematic Delay (Msec)     | 250         |              |

| Security Option            | Setup       |              |

| APIC Mode                  | Enabled     |              |

| MPS Version Control for OS | 1.4         |              |

| OS Select For DRAM>64MB    | Non-OS2     |              |

| Small Logo (EPA) Show      | Disabled    |              |

|                            |             |              |

#### **CPU Feature**

Press Enter to configure the settings relevant to CPU Feature.

### Hard Disk Boot Priority

With the field, there is the option to choose, aside from the hard disks connected, "Bootable add-in Cards" which refers to other external devices.

#### **Virus Warning**

If this option is enabled, an alarm message will be displayed when trying to write on the boot sector or on the partition table on the disk, which is typical of the virus.

### CPU L1 and L2 Cache

Cache memory is additional memory that is much faster than conventional DRAM (system memory). CPUs from 486-type on up contain internal cache memory, and most, but not all, modern PCs have additional (external) cache memory. When the CPU requests data, the system transfers the requested data from the main DRAM into cache memory, for even faster access by the CPU. These items allow you to enable (speed up memory access) or disable the cache function. By default, these items are Enabled.

MI920 User's Manual

### **Quick Power On Self Test**

When enabled, this field speeds up the Power On Self Test (POST) after the system is turned on. If it is set to *Enabled*, BIOS will skip some items.

### First/Second/Third Boot Device

These fields determine the drive that the system searches first for an operating system. The options available include *LS120*, *Hard Disk*, *CDROM*, *ZIP100*, *USB-FDD*, *USB-ZIP*, *USB-CDROM*, *LAN* and *Disable*.

## **Boot Other Device**

These fields allow the system to search for an OS from other devices other than the ones selected in the First/Second/Third Boot Device.

#### **Boot Up NumLock Status**

This allows you to activate the NumLock function after you power up the system.

# Gate A20 Option

This field allows you to select how Gate A20 is worked. Gate A20 is a device used to address memory above 1 MB.

#### **Typematic Rate Setting**

When disabled, continually holding down a key on your keyboard will generate only one instance. When enabled, you can set the two typematic controls listed next. By default, this field is set to *Disabled*.

### Typematic Rate (Chars/Sec)

When the typematic rate is enabled, the system registers repeated keystrokes speeds. Settings are from 6 to 30 characters per second.

### **Typematic Delay (Msec)**

When the typematic rate is enabled, this item allows you to set the time interval for displaying the first and second characters. By default, this item is set to *250msec*.

# **Security Option**

This field allows you to limit access to the System and Setup. The default value is *Setup*. When you select *System*, the system prompts for the User Password every time you boot up. When you select *Setup*, the system always boots up and prompts for the Supervisor Password only when the Setup utility is called up.

28

29

#### **APIC Mode**

APIC stands for Advanced Programmable Interrupt Controller. The default setting is *Enabled*.

### **MPS Version Control for OS**

This option is specifies the MPS (Multiprocessor Specification) version for your operating system. MPS version 1.4 added extended configuration tables to improve support for multiple PCI bus configurations and improve future expandability. The default setting is *1.4*.

#### OS Select for DRAM > 64MB

This option allows the system to access greater than 64MB of DRAM memory when used with OS/2 that depends on certain BIOS calls to access memory. The default setting is *Non-OS/2*.

#### Small Logo (EPA) Show

The EPA logo appears at the right side of the monitor screen when the system is boot up. The default setting is *Disabled*.

# **Advanced Chipset Features**

This Setup menu controls the configuration of the chipset.

Phoenix - AwardBIOS CMOS Setup Utility

| Advanced Chipset Features                                                                                                                                                                                                                             |                                                                                                                  |              |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|--------------|

| DRAM Timing Selectable                                                                                                                                                                                                                                | By SPD                                                                                                           | ITEM HELP    |

| CAS Latency Time                                                                                                                                                                                                                                      | 3                                                                                                                | Menu Level > |

| DRAM RAS# to CAS# Delay                                                                                                                                                                                                                               | 3                                                                                                                |              |

| DRAM RAS# Precharge                                                                                                                                                                                                                                   | 3                                                                                                                |              |

| Precharge delay (tRAS)                                                                                                                                                                                                                                | 9                                                                                                                |              |

| System Memory Frequency                                                                                                                                                                                                                               | 400MHZ                                                                                                           |              |

| SLP_S4# Assertion Width                                                                                                                                                                                                                               | 1 to 2 Sec                                                                                                       |              |

| System BIOS Cacheable                                                                                                                                                                                                                                 | Enabled                                                                                                          |              |

| Video BIOS Cacheable                                                                                                                                                                                                                                  | Ensabled                                                                                                         |              |

| Memory Hole at 15M-16M                                                                                                                                                                                                                                | Disabled                                                                                                         |              |

| PCI Express Root Port Func                                                                                                                                                                                                                            | Press Enter                                                                                                      |              |

| ** VGA Setting **<br>PEG/On Chip VGA Control<br>On-Chip Frame Buffer Size<br>DVMT Mode<br>DVMT/FIXED memory Size<br>SDVO Device Setting<br>SDVO LVDS Protocol<br>SDVO Panel Number<br>Boot Display<br>Panel Scaling<br>TV Standard<br>Video Connector | Auto<br>8MB<br>DVMT<br>128MB<br>LVDS + DVI<br>1CH SPGW, 24bit<br>1024x768<br>CRT+DVI<br>Auto<br>Off<br>Automatic |              |

| TV Format                                                                                                                                                                                                                                             | Auto                                                                                                             |              |

| Onboard PCI-E LAN                                                                                                                                                                                                                                     | Enable                                                                                                           |              |

| LAN PXE Option ROM                                                                                                                                                                                                                                    | All Disable                                                                                                      |              |

| •                                                                                                                                                                                                                                                     |                                                                                                                  |              |

#### **DRAM Timing Selectable**

This option refers to the method by which the DRAM timing is selected. The default is *By SPD*.

#### **CAS Latency Time**

You can configure CAS latency time in HCLKs as 3 or 4 or 5. The system board designer should set the values in this field, depending on the DRAM installed. Do not change the values in this field unless you change specifications of the installed DRAM or the installed CPU.

#### DRAM RAS# to CAS# Delay

This option allows you to insert a delay between the RAS (Row Address Strobe) and CAS (Column Address Strobe) signals. This delay occurs when the SDRAM is written to, read from or refreshed. Reducing the delay improves the performance of the SDRAM.

30

#### **DRAM RAS# Precharge**

This option sets the number of cycles required for the RAS to accumulate its charge before the SDRAM refreshes. The default setting for the Active to Precharge Delay is *3*.

#### Precharge Delay (tRAS)

The default setting for the Precharge Delay is 9.

#### System Memory Frequency

The default setting is 400MHz.

#### SLP\_S4# Assertion Width

The default setting is 1 to 2 Sec.

#### System BIOS Cacheable

The setting of *Enabled* allows caching of the system BIOS ROM at F000h-FFFFFh, resulting in better system performance. However, if any program writes to this memory area, a system error may result.

#### Video BIOS Cacheable

The Setting *Enabled* allows caching of the video BIOS ROM at C0000h-F7FFFh, resulting in better video performance. However, if any program writes to this memory area, a system error may result.

#### Memory Hole At 15M-16M

In order to improve performance, certain space in memory can be reserved for ISA cards. This memory must be mapped into the memory space below 16 MB. The choices are *Enabled* and *Disabled*.

### **On-Chip VGA Setting**

The fields under the On-Chip VGA Setting and their default settings are: PEG/On Chip VGA Control: Auto On-Chip Frame Buffer Size: 8MB DVMT Mode: DVTM DVMT/Fixed Memory Size: 128MB SDVO Device Setting: LVDS+DVI SDVO LVDS Protocol: 1Ch SPGW, 24bit SDVO Panel Number: 1024x768 Boot Display: CRT+DVI Panel Scaling: Auto TV Standard: Off Video Connector: Automatic TV Format: Auto

MI920 User's Manual

# **Panel Scaling**

The default setting is Auto. The options available include On and Off.

# **Onboard PCI-E LAN**

By default, this setting is enabled.

LAN PXE Option ROM By default, this setting is All Disabled. The options available include All Disabled and ICH6 integrated Lan.

32

## **Integrated Peripherals**

This section sets configurations for your hard disk and other integrated peripherals. The first screen shows three main items for user to select. Once an item selected, a submenu appears. Details follow.

Phoenix - AwardBIOS CMOS Setup Utility

| integrated relipiterais        |             |              |

|--------------------------------|-------------|--------------|

| OnChip IDE Device              | Press Enter | ITEM HELP    |

| Onboard Device                 | Press Enter | Menu Level > |

| SuperIO Device                 | Press Enter |              |

| 2 <sup>nd</sup> SuperIO Device | Press Enter |              |

#### Phoenix - AwardBIOS CMOS Setup Utility OnChip IDE Device

|                                    | OnChip IDE Device |              |

|------------------------------------|-------------------|--------------|

| IDE HDD Block Mode                 | Enabled           | ITEM HELP    |

| On-chip Primary PCI IDE            | Enabled           |              |

| IDE Primary Master PIO             | Auto              | Menu Level > |

| IDE Primary Slave PIO              | Auto              |              |

| IDE Primary Master UDMA            | Auto              |              |

| IDE Primary Slave UDMA             | Auto              |              |

| On-Chip Secondary PCI IDE          | Enabled           |              |

| IDE Secondary Master PIO           | Auto              |              |

| IDE Secondary Slave PIO            | Auto              |              |

| IDE Secondary Master UDMA          | Auto              |              |

| IDE Secondary Slave UDMA           | Auto              |              |

| *** On-Chip Serial ATA Setting *** |                   |              |

| SATA Mode                          | IDE               |              |

| On-Chip Serial ATA                 | Auto              |              |

| PATA IDE Mode                      | Secondary         |              |

| SATA port                          | P0, P2 is Primary |              |

|                                    |                   |              |

## Phoenix - AwardBIOS CMOS Setup Utility

| Olibbald Device                            |                     |              |

|--------------------------------------------|---------------------|--------------|

| USB Controller                             | Enabled             | ITEM HELP    |

| USB 2.0 Controller<br>USB Keyboard Support | Enabled<br>Ensabled | Menu Level > |

| Azalia/AC97 Audio Select                   | Auto                |              |

#### Phoenix - AwardBIOS CMOS Setup Utility SuperIO Device

| POWER ON Function     | BUTTON ONLY | ITEM HELP    |

|-----------------------|-------------|--------------|

| KB Power ON Password  | Enter       | Menu Level > |

| Hot Key power ON      | Ctrl-F1     |              |

| Onboard Serial Port 1 | 3F8/IRQ4    |              |

| Onboard Serial Port 2 | 2F8/IRQ3    |              |

| PWRON After PWR-Fail  | Off         |              |

MI920 User's Manual

Phoenix - AwardBIOS CMOS Setup Utility

| 2 <sup>nd</sup> Superio Device |       |              |

|--------------------------------|-------|--------------|

| Onboard Serial Port 3          | 2B0H  | ITEM HELP    |

| Serial Port 3 Use IRQ          | IRQ11 | Menu Level > |

| Onboard Serial Port 4          | 2B8H  |              |

| Serial Port 4 Use IRQ          | IRQ10 |              |

|                                |       |              |

#### **IDE HDD Block Mode**

This field allows your hard disk controller to use the fast block mode to transfer data to and from your hard disk drive.

#### **On-chip Primary PCI IDE Enabled**

This field, by default, is enabled

## **OnChip Primary/Secondary PCI IDE**

The integrated peripheral controller contains an IDE interface with support for two IDE channels. Select *Enabled* to activate each channel separately.

### IDE Primary/Secondary Master/Slave PIO

These fields allow your system hard disk controller to work faster. Rather than have the BIOS issue a series of commands that transfer to or from the disk drive, PIO (Programmed Input/Output) allows the BIOS to communicate with the controller and CPU directly.

The system supports five modes, numbered from 0 (default) to 4, which primarily differ in timing. When Auto is selected, the BIOS will select the best available mode.

#### IDE Primary/Secondary Master/Slave UDMA

These fields allow your system to improve disk I/O throughput to 33Mb/sec with the Ultra DMA/33 feature. The options are *Auto* and *Disabled*.

34

#### **On-Chip Serial ATA Setting**

The fields under the SATA setting includes On-Chip Serial ATA (Auto), PATA IDE Mode (Secondary) and SATA Port (PO, P2 is Primary).

#### **USB** Controller

The options for this field are *Enabled* and *Disabled*. By default, this field is set to *Enabled*.

#### **USB 2.0 Controller**

The options for this field are *Enabled* and *Disabled*. By default, this field is set to *Enabled*. In order to use USB 2.0, necessary OS drivers must be installed first. *Please update your system to Windows 2000 SP4 or Windows XP SP2*.

#### **USB Keyboard Support**

The options for this field are *Enabled* and *Disabled*. By default, this field is set to *Enabled*.

### Azalia/AC97 Audio Select

This field, by default, is set to Auto.

#### **Power ON Function**

This field is related to how the system is powered on - such as with the use of conventional power button, keyboard or hot keys. The default is *BUTTON ONLY*.

#### **KB Power ON Password**

This field allows users to set the password when keyboard power on is the mode of the Power ON function.

#### Hot Key Power ON

This field sets certain keys, also known as hot keys, on the keyboard that can be used as a 'switch' to power on the system.

MI920 User's Manual

## **Onboard Serial Port**

These fields allow you to select the onboard serial ports and their addresses. The default values for these ports are:

| Serial Port 1 | 3F8/IRQ4  |

|---------------|-----------|

| Serial Port 2 | 2F8/IRQ3  |

| Serial Port 3 | 2B0/IRQ11 |

| Serial Port 4 | 2B8/IRQ10 |

### **PWRON After PWR-Fail**

This field sets the system power status whether *on or off* when power returns to the system from a power failure situation.

36

## **Power Management Setup**

Phoenix - AwardBIOS CMOS Setup Utility

|                                  | Power Management Setup |              |

|----------------------------------|------------------------|--------------|

| ACPI Function                    | Enabled                | ITEM HELP    |

| ACPI Suspend                     | S1(POS)                | Menu Level > |

| RUN VGABIOS if S3 Resume         | Auto                   |              |

| Power Management                 | User Define            |              |

| Video Off Method                 | V/H SYNC+Blank         |              |

| Video Off In Suspend             | Yes                    |              |

| Suspend Type                     | Stop Grant             |              |

| Modem Use IRQ                    | 3                      |              |

| Suspend Mode                     | Disabled               |              |

| HDD Power Down                   | Disabled               |              |

| Soft-Off by PWR-BTTN             | Instant-Off            |              |

| Wake-Up by PCI Card              | Disabled               |              |

| Power On by Ring                 | Disabled               |              |

| Resume by Alarm                  | Disabled               |              |

| Date (of Month) Alarm            | 0                      |              |

| Time (hh:mm:ss) Alarm            | 0:0:0                  |              |

| ** Reload Global Timer Events ** |                        |              |

| Primary IDE 0                    | Enabled                |              |

| Primary IDE 1                    | Enabled                |              |

| Secondary IDE 0                  | Enabled                |              |

| Secondary IDE 1                  | Enabled                |              |

| FDD, COM, LPT Port               | Enabled                |              |

| PCI PIRQ[A-D] #                  | Enabled                |              |

#### **ACPI Function**

Enable this function to support ACPI (Advance Configuration and Power Interface).

#### **ACPI Suspend**

The default setting of the ACPI Suspend mode is S1(POS).

### **RUN VGABIOS if S3 Resume**

The default setting of this field is Auto.

### **Power Management**

This field allows you to select the type of power saving management modes. There are four selections for Power Management.

Min. Power Saving Max. Power Saving User Define Minimum power management Maximum power management. Each of the ranges is from 1 min. to 1hr. Except for HDD Power Down which ranges from 1 min. to 15 min.

MI920 User's Manual

#### Video Off Method

This field defines the Video Off features. There are three options.

| V/H SYNC + Blank | Default setting, blank the screen and turn |

|------------------|--------------------------------------------|

|                  | off vertical and horizontal scanning.      |

| DPMS             | Allows BIOS to control the video display.  |

| Blank Screen     | Writes blanks to the video buffer.         |

#### Video Off In Suspend

When enabled, the video is off in suspend mode. The default setting is *Yes*.

#### Suspend Type

The default setting for the Suspend Type field is Stop Grant.

#### Modem Use IRQ

This field sets the IRQ used by the Modem. By default, the setting is 3.

## **Suspend Mode**

When enabled, and after the set time of system inactivity, all devices except the CPU will be shut off.

#### **HDD Power Down**

When enabled, and after the set time of system inactivity, the hard disk drive will be powered down while all other devices remain active.

#### Soft-Off by PWRBTN

This field defines the power-off mode when using an ATX power supply. The *Instant Off* mode allows powering off immediately upon pressing the power button. In the *Delay 4 Sec* mode, the system powers off when the power button is pressed for more than four seconds or enters the suspend mode when pressed for less than 4 seconds.

### Wake up by PCI Card

By default, this field is Disabled.

#### Power On by Ring

This field enables or disables the power on of the system through the modem connected to the serial port or LAN.

38

## **Resume by Alarm**

This field enables or disables the resumption of the system operation. When enabled, the user is allowed to set the *Date* and *Time*.

## **Reload Global Timer Events**

The HDD, FDD, COM, LPT Ports, and PCI PIRQ are I/O events that can prevent the system from entering a power saving mode or can awaken the system from such a mode. When an I/O device wants to gain the attention of the operating system, it signals this by causing an IRQ to occur. When the operating system is ready to respond to the request, it interrupts itself and performs the service.

## **PNP/PCI** Configurations

This option configures the PCI bus system. All PCI bus systems on the system use INT#, thus all installed PCI cards must be set to this value. Phoenix - AwardBIOS CMOS Setup Utility

|                                                        | PnP/PCI Configurations |                                                |

|--------------------------------------------------------|------------------------|------------------------------------------------|

| Init Display First                                     | PCI Slot               | ITEM HELP                                      |

| Reset Configuration Data                               | Disabled               |                                                |

|                                                        |                        | Menu Level                                     |

| Resources Controlled By                                | Auto (ESCD)            |                                                |

| IRQ Resources                                          | Press Enter            | Select Yes if you are<br>using a Plug and Play |

| DCIA/CA Delette Speen                                  | Disabled               | capable operating                              |

| PCI/VGA Palette Snoop                                  | Auto                   | system Select No if                            |

| INT Pin 1 Assignment                                   | Auto                   | you need the BIOS to                           |

| INT Pin 2 Assignment                                   |                        | configure non-boot                             |

| INT Pin 3 Assignment                                   | Auto                   | devices                                        |

| INT Pin 4 Assignment                                   | Auto                   |                                                |

| INT Pin 5 Assignment                                   | Auto                   |                                                |

| INT Pin 6 Assignment                                   | Auto                   |                                                |

| INT Pin 7 Assignment                                   | Auto                   |                                                |

| INT Pin 8 Assignment                                   | Auto                   |                                                |

| **PCI Express relative items**<br>Maximum Payload Size | 4096                   |                                                |

| ,                                                      |                        |                                                |

#### **Init Display First**

The default setting is *PCI Card*.

#### **Reset Configuration Data**

This field allows you to determine whether to reset the configuration data or not. The default value is *Disabled*.

## **Resources Controlled by**

This PnP BIOS can configure all of the boot and compatible devices with the use of a PnP operating system such as Windows 95.

### **PCI/VGA Palette Snoop**

Some non-standard VGA display cards may not show colors properly. This field allows you to set whether or not MPEG ISA/VESA VGA cards can work with PCI/VGA. When this field is enabled, a PCI/VGA can work with an MPEG ISA/VESA VGA card. When this field is disabled, a PCI/VGA cannot work with an MPEG ISA/VESA card.

### **Maximum Payload Size**

The default setting of the PCI Express Maximum Payload Size is 4096.

40

#### **PC Health Status**

This section shows the parameters in determining the PC Health Status. These parameters include temperatures, fan speeds and voltages.

|                         | PC Health Status |              |

|-------------------------|------------------|--------------|

| Shutdown Temperature    | Disabled         | ITEM HELP    |

| CPU Warning Temperature | Disabled         |              |

| Current System Temp     | 45°C/113°F       | Menu Level > |

| Current CPU Temp        | 45°C/113°F       |              |

| FAN2 Speed              | 5400 RPM         |              |

| FAN1 Speed              | 5400 RPM         |              |

| Vcore                   | 0.94 V           |              |

| +12 V                   | 11.92 V          |              |

| +1.8V                   | 1.83V            |              |

| +5 V                    | 5.25 V           |              |

| +3.3V                   | 3.37V            |              |

| VBAT (V)                | 3.21 V           |              |

| 5VSB(V)                 | 5.50 V           |              |

| Smart FAN1 Temperature  | Disabled         |              |

| FAN1 Tolerance Value    | 1                |              |

Phoenix - AwardBIOS CMOS Setup Utility

#### **Shutdown Temperature**

This field allows the user to set the temperature by which the system automatically shuts down once the threshold temperature is reached. This function can help prevent damage to the system that is caused by overheating.

#### **CPU Warning Temperature**

This field allows the user to set the temperature so that when the temperature is reached, the system sounds a warning. This function can help prevent damage to the system that is caused by overheating.

#### **Temperatures/Voltages**

These fields are the parameters of the hardware monitoring function feature of the motherboard. The values are read-only values as monitored by the system and show the PC health status.

#### Smart FAN1 Temperature

This field enables or disables the smart fan feature. At a certain temperature, the fan starts turning. Once the temperature drops to a certain level, it stops turning again.

## **FAN1** Tolerance Value

The default value is 1.

MI920 User's Manual

## Frequency/Voltage Control

This section shows the user how to configure the processor frequency.

Phoenix - AwardBIOS CMOS Setup Utility

|                           | Frequency/voltage Control |              |

|---------------------------|---------------------------|--------------|

| Auto Detect PCI Clk       | Disabled                  | ITEM HELP    |

| Spread Spectrum Modulated | Disabled                  | Menu Level > |

|                           |                           |              |

## Auto Detect PCI Clk

This field enables or disables the auto detection of the PCI clock.

## **Spread Spectrum Modulated**

This field sets the value of the spread spectrum. The default setting is *Disabled*. This field is for CE testing use only.

### Load Fail-Safe Defaults

This option allows you to load the troubleshooting default values permanently stored in the BIOS ROM. These default settings are non-optimal and disable all high-performance features.

#### Load Optimized Defaults

This option allows you to load the default values to your system configuration. These default settings are optimal and enable all high performance features.

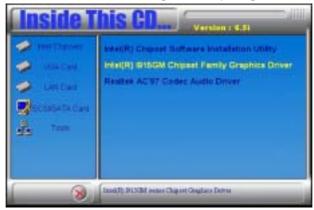

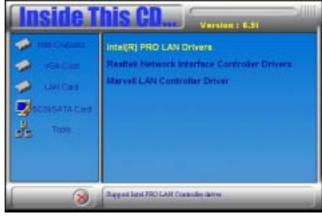

#### Set Supervisor Password